The RISC-V architecture has gained significant attention in recent years due to its open-source nature and potential for widespread adoption. However, one of the main challenges in adopting RISC-V is the lack of a mature software ecosystem compared to established architectures such as ARM and x86. The binary translation is an effective methodology that can address such challenge.

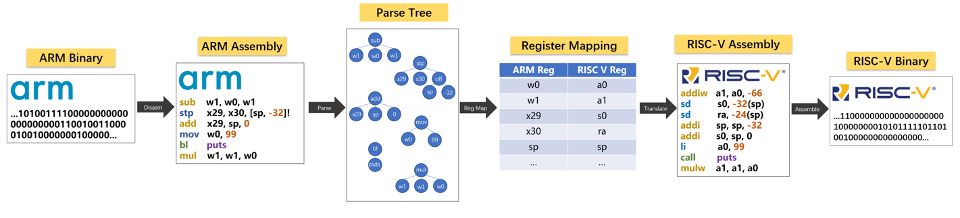

We thus propose a novel binary translator to automatically convert existing applications of ARM or x86 to RISC-V. The translator is designed to facilitate the adoption of RISC-V architecture by providing a seamless transition of existing software to RISC-V. The use of LLVM IR as a bridge between the source and target architectures allows us to leverage the mature LLVM toolchain and facilitate the translation process. LLVM IR provides a high-level representation of the code that is independent of the source and target architectures, making it easier to translate between different architectures. This reduces the complexity of the translation process and makes it more efficient. Our approach is based on a new paradigm that can automatically learn and generate the mapping rules of assembly instructions. The mapping rules are learned from a large dataset of existing software, which allows the translator to accurately and efficiently translate the software. To ensure the performance of the translated code, we have adopted the SBT paradigm. The SBT paradigm allows us to selectively optimize the performance-critical parts of the code, while leaving the non-critical parts unoptimized. This approach reduces the overall time and effort required to optimize the code while still maintaining the performance of the translated software.