RISC-V 2022 North America Global Summit

The four-days RISC-V 2022 North America Global Summit was held in San Jose, California, December 12th-15th, 2022. The conference schedule includes:

· RISC-V members day meeting

· RISC-V Future Watch featuring breaking news on products, technology, ecosystem expansion, etc.

· Technical and industry topics meetings

· Innovative research presentation

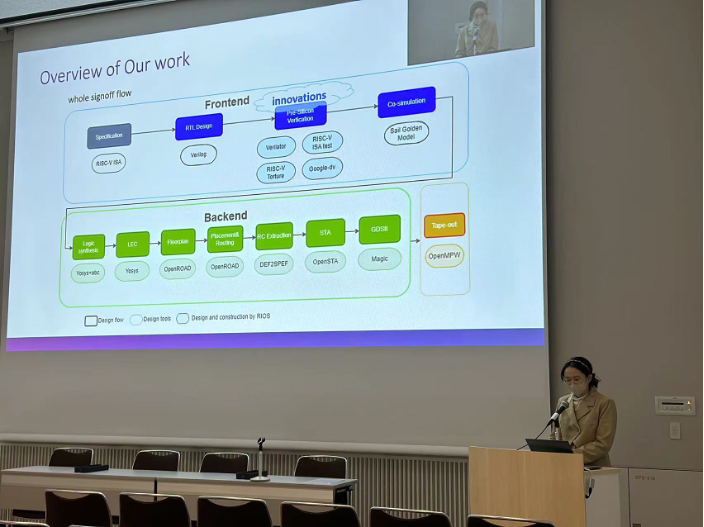

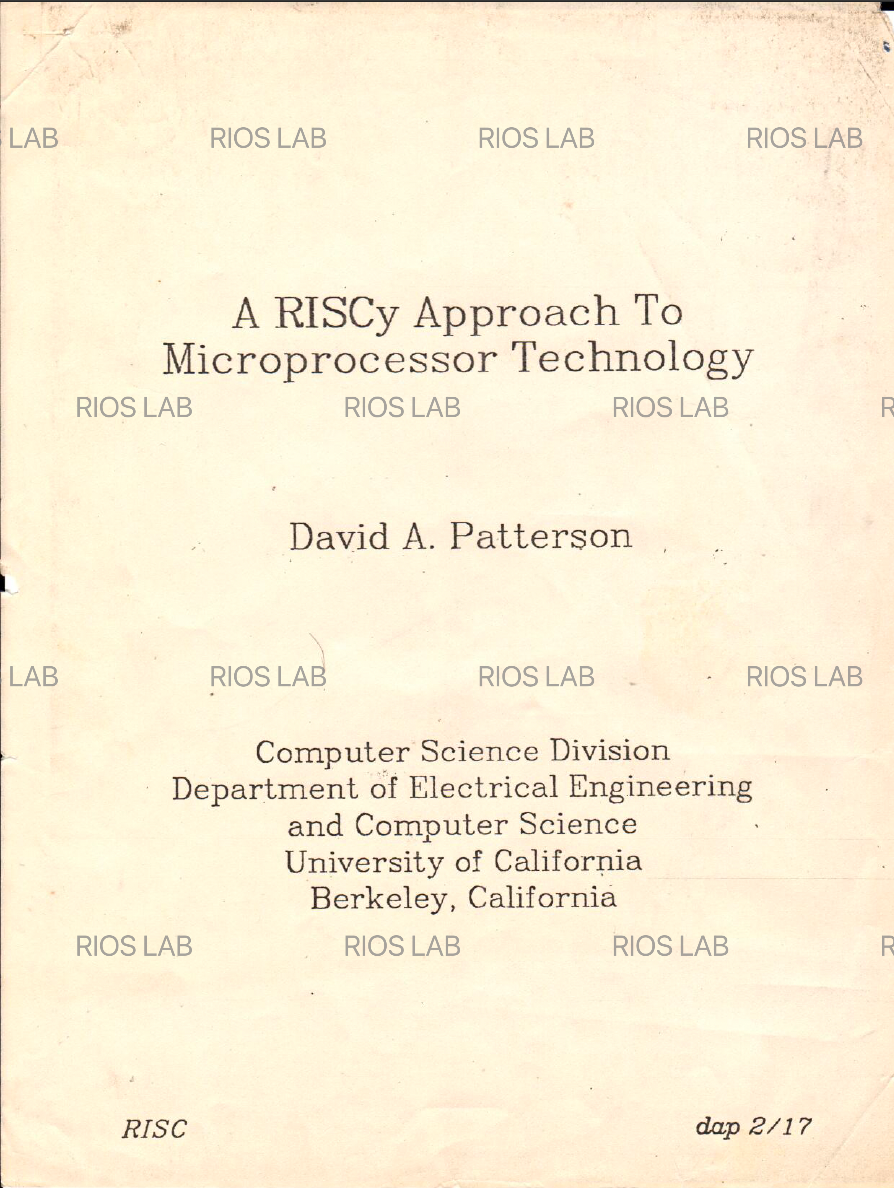

Automatic Test Generation and Verification for RISC-V Vector Extension, from RISC-V International Open Source (RIOS) laboratory, was admitted by RISC-V Summit North America 2022. Dr. Wang Yi and Mr. Hu Shenwei were honored to attend the conference as speakers and had an in-depth discussion online to communicate with industry professionals.

The RISC-V Vector Extended Instruction Set (RVV) version 1.0 has been introduced for high-performance execution of vectorized computing. However, the RVV introduces 217 new instructions, seven new CSRS, and seven configuration parameters. The complexity makes it difficult for developers to produce a test suite, especially because of the number of different RVV parameter configurations (vlen, vsew, vmul, etc.) that combine with each other.

To solve this problem, RIOS Lab, in collaboration with the RISC-V Foundation, designed an RVV test generator for RISC-V community that can be configured with a combination of parameters. We first designed and implemented the RVV Sail Model as the golden model for executing RVV instructions. With Sail model ‘s support, we further developed a configurable test generator that generates quantifiable coverage test sets for RISC-V vector extensions. The user can select the instruction to be tested, set the configuration parameter combination, and then automatically generate the associated tests.

The whole process of test production and usage is compatible with the latest RISCOF toolchain and can be tested simultaneously with vector extension and other extension test sets in the same environment. We also demonstrated our RVV support for RISCV-ISAC and RISCOF to obtain quantitative coverage reports.

Currently, the Sail RVV adaptation has pushed the Pull Request to the official repository and is being checked by RISC-V Foundation. The test generator and RISC-V ISAC are undergoing final feedback and adjustment with RISC-V Foundation, and it will be released soon after the improvement.

Original link: https://mp.weixin.qq.com/s/S3xqKSUvZJV7YaWixYD-_g

Recommended Reading