PicoRio is an open-source CPU project developed by the RISC-V International Open Source (RIOS) laboratory with the goal of creating an open, affordable, Linux-capable RISC-V hardware platform to help software developers and elevate the RISC-V software and hardware ecosystem collaboratively with both academia and industry.

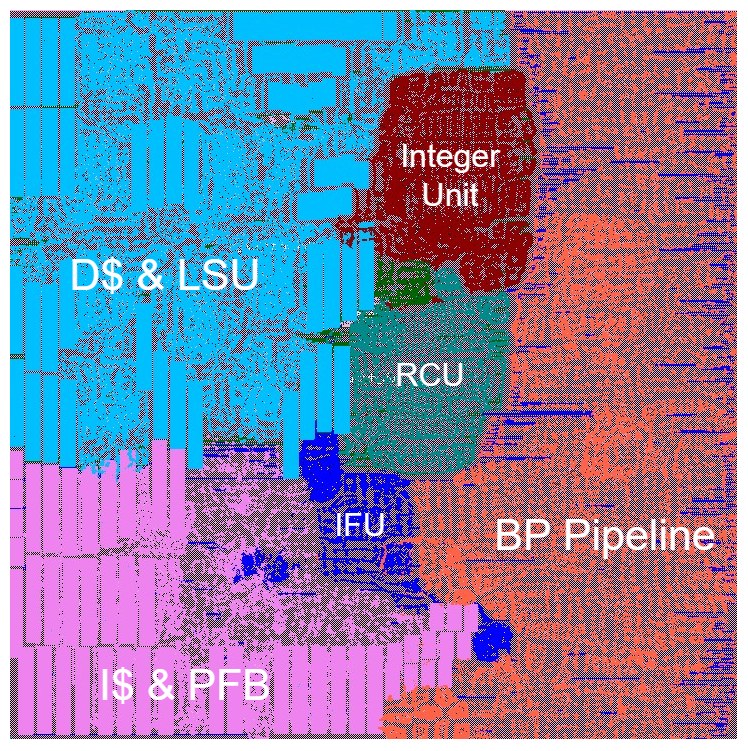

PicoRio 2.0 CPU is a RV64GC (IMAFDC) core with 13+ stages superscalar out-of-order pipeline. The front-end features two-level branch prediction, and decoupled fetch pipeline and predict pipeline. The PicoRio 2.0 system is a scalable multi-core design for server application with 8/16-core configuration. The system features a coherent network, scalable cache coherence support, mesh linker for on-die network scale-up, and die linker for inter-die network scale-up. The PicoRio 2.0 CPU tile includes a PicoRio 2 core, configurable core number per tile (1~4 cores), configurable exclusive private L2 cache, and configurable NoC Router (0~4 local device ports).