Overview

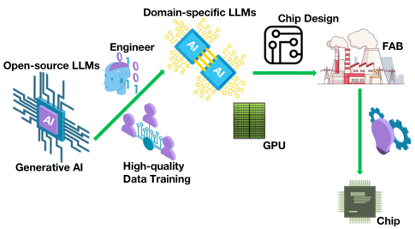

The Generative AI for Chip Design project at RIOS Lab is at the forefront of merging artificial intelligence (AI) with the intricate world of chip design. Our mission is to harness the power of generative AI models, such as open-source Large Language Models (LLMs) like Llama2 and Mixtral, and tailor them specifically for the challenges and opportunities within the semiconductor industry. By fine-tuning these models on a rich dataset of Verilog code and other domain-specific data, we aim to create specialized tools that can automate and innovate the processes involved in designing chips and System on Chips (SoCs).

Research Focus Areas

Fine-Tuning LLMs for Chip Design

We start with open-source LLMs, recognizing their vast potential. The process of fine-tuning these models with additional, highly specialized Verilog data allows us to create domain-specific LLMs that understand the intricacies of chip design. This initiative not only streamlines the design process but also significantly reduces the entry barrier for complex chip design tasks.

Automation of Chip Design Tasks

Our laboratory focuses on automating time-consuming chip design tasks that traditionally require extensive human intervention. This includes tasks that involve interfacing with both natural languages and programming languages, thereby generating Register Transfer Level (RTL) code for simple to complex design modules and scripting for Electronic Design Automation (EDA) tools.

Overcoming Data Scarcity and Privacy Challenges

A major focus of our work is to solve the dual challenges of training data scarcity and privacy concerns in the semiconductor industry. We employ innovative strategies to generate synthetic data and use privacy-preserving techniques to enable the training of potent AI models without compromising sensitive information.

Resource Optimization

Understanding the constraints of GPU resources essential for training sophisticated models, our research also delves into optimizing the use of computational resources. This involves developing more efficient algorithms that can run on limited resources without sacrificing performance.

VLSI Bug Summarization and Analysis

We leverage generative AI to summarize and analyze bugs in Very Large Scale Integration (VLSI) designs. This approach helps in quickly identifying potential issues, speeding up the debug process, and ensuring a higher quality of the final chip design.

Design Debug and PPA Prediction

Our research extends to utilizing AI for design debug and Predicting Power, Performance, and Area (PPA) of chip designs. By predicting these critical parameters early in the design cycle, we can significantly enhance the productivity and efficiency of chip design projects.

Enhancing Chip Design Productivity

Ultimately, the goal of our research is to significantly improve chip design productivity. By automating routine tasks, providing early insights into potential design issues, and optimizing the design process, we aim to free human designers to focus on the most innovative aspects of chip design.

Industrial Collaboration

We are committed to translating our research findings into practical solutions for the industry. Collaboration with chip and SoC design companies ensures that our innovations are grounded in real-world needs and can directly contribute to advancing the state of the art in chip design.

Conclusion

At the Generative AI for Chip Design Laboratory, we are not just envisioning the future of chip design; we are actively creating it. Through our cutting-edge research and industry collaborations, we aim to lead the way in making chip design more efficient, innovative, and accessible.