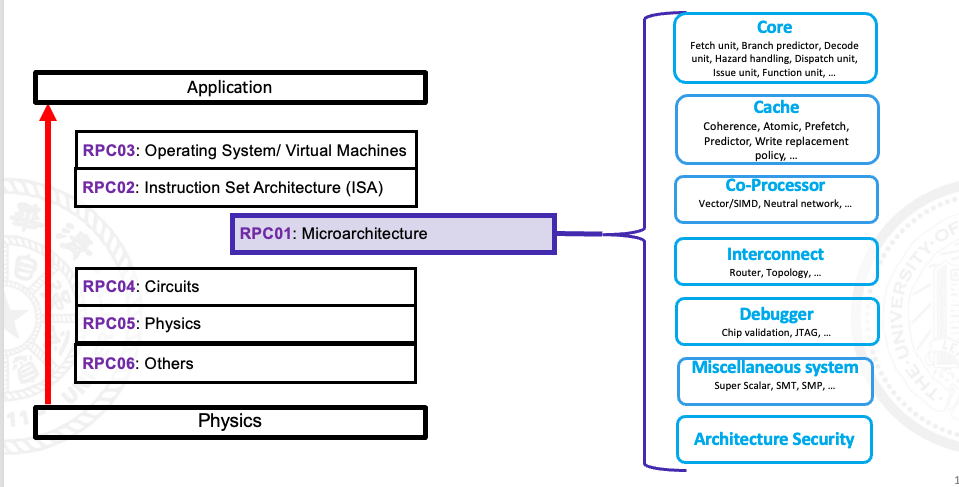

Tremendous attractions for RISC-V have driven needs for its effective adoption by industry due to its superb free, open, modular and secure nature, as well as its simple and elegant core and large international community. However, during the development of RISC-V, potential patent infringement and implement litigation might occur at processor architecture and microarchitecture. Thus, a secured legal infrastructure against patent troll and pitfalls contributes significantly to the growth of RISC-V community, and it’s also one of the key tools our RIOS Lab is building under the guidance of technical experts. We systematically analyzed thousands of patents from MIPS and ARM, and established a new classification system, RPC (RIOS Patent Classification), in favor of CPU domain knowledge which the existing systems IPC and CPC are in lack of, based on different technical and functional modules during processor design and development process, statistical landscape analysis results of which outshined those based on IPC and CPC. Based on these RPC categories and resources from Google Patent, RIOS Lab also built its own microprocessor-domain patent database infrastructure with machine learning and artificial intelligence (AI) assisted patent recommendation engine.

In addition, legal status, patent assignment, active patents owners, application and grant rate, imminent expiration, number of citations and independent claims, and litigation cases were all investigated. Through this work RIOS Lab would dedicate a defensive and monitoring system against potential IP risks for RISC-V processor and open-source hardware implementations, and make patent freedom and open source safely achieved in RISC-V ecosystem.

You can find more information about RPC classification here: